2.2. Vitis HLS Development Flow#

As discussed in Section 2, we are responsible for the macro-architecture design of a DSP kernel in the HLS development process. Vitis HLS will then automate the micro-architecture design of the DSP kernel and synthesize the RTL implementation following the steps described in Section 2.1.

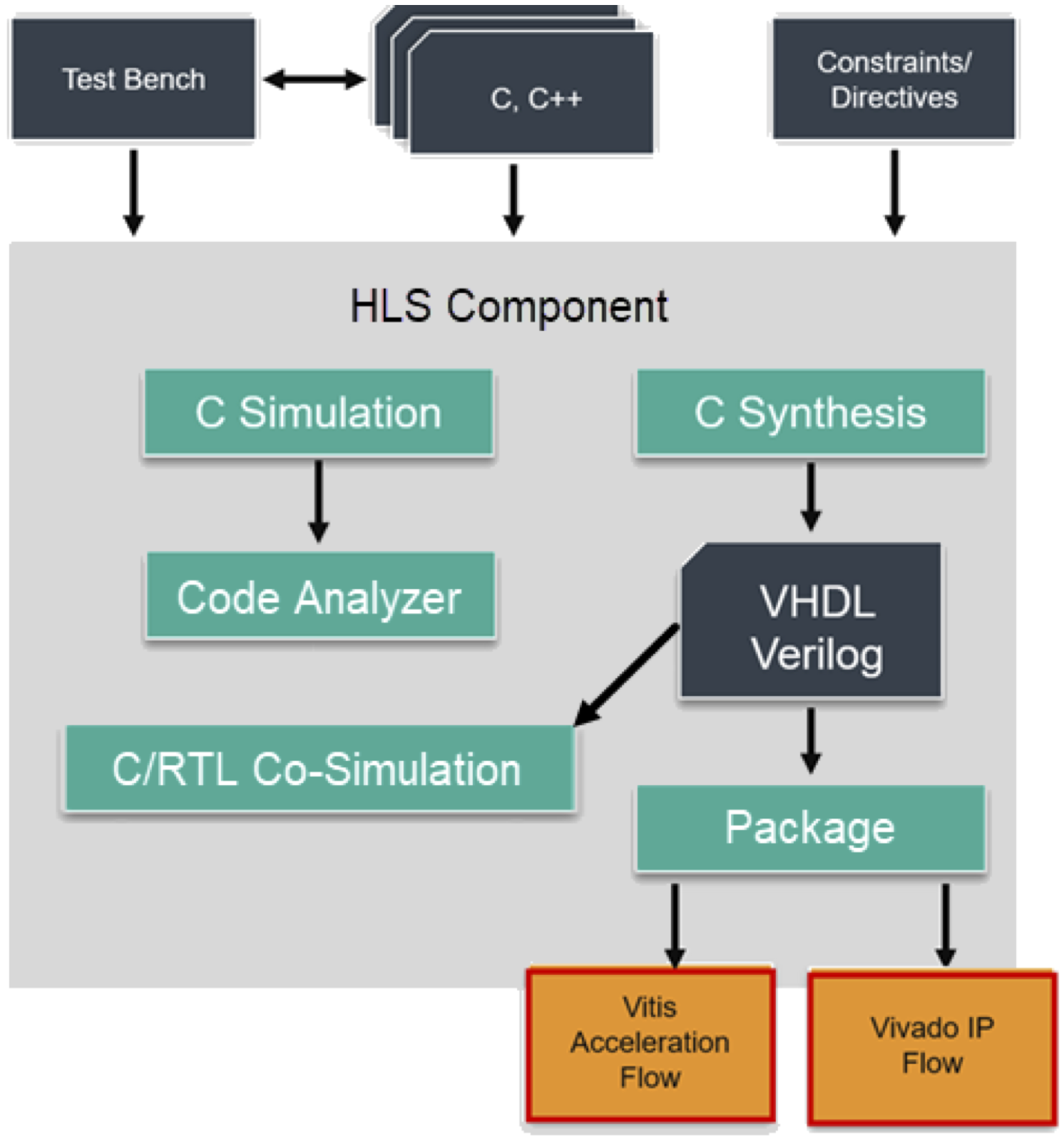

The standard sequence of steps to use Vitis HLS for DSP kernel development in the VAAD flow are listed blow:

C/C++ Kernel Coding: Develop the C/C++ specification of the DSP kernel, and specify the external interfaces, design constraints, and directives.

C-Simulation: Verify the functionality of the C/C++ kernel code with the C/C++ test bench.

Code Analysis: Analyze the performance, parallelism, and legality of the C/C++ kernel code.

C-Synthesis: Generate the RTL specification for the given clock speed and input constraints using the v++ compiler.

C/RTL Co-Simulation: Verify the RTL code generated using the C/C++ test bench, and review the HLS synthesis and implementation timing reports. If necessary, re-run previous steps until performance goals are met.

Package: Generate the DSP kernel object (

.xo) for use in the VAAD flow.

Fig. 2.3 Steps in the Vitis HLS development flow (image taken from [AMD-Xilinx24c])#

In Section 3, we will briefly describe some basic design principles, considerations, and techniques in writing optimized C/C++ code for DSP development using HLS.