1.3. Vitis Application Acceleration Development#

As discussed in Section 1.2.2, we have to program the different compute components and construct interfaces (both hardware and software) between them in the typical embedded system development process. In particular, the development of the AXI4 interfaces between the DSP kernels and the DMA interface with the global memory can be rather laborious. While the implementation of these interfaces may serve as good design exercises in a digital design class, it is not exactly the focus of what we want to do here, namely DSP kernel implementation.

In order to simplify our development process, we will employ the following approach:

Follow the Vitis Application Acceleration Development (VAAD) Flow [AMD-Xilinx24b].

Use HLS to develop DSP kernels under the VAAD flow. We will discuss more about the HLS design process in Section 2.

1.3.1. Vitis Application Acceleration Development Flow#

The VAAD flow [AMD-Xilinx24b] is essentially a design process that allows developers to focus on developing the core functionalities of the PL kernels while the development of the required interfaces is all automated by Vitis. For embedded system development, the VAAD flow corresponds to the Vitis Integrated Flow since Vitis v2024.2 [AMD-Xilinx24a].

The components that constitute a VAAD flow inlcude:

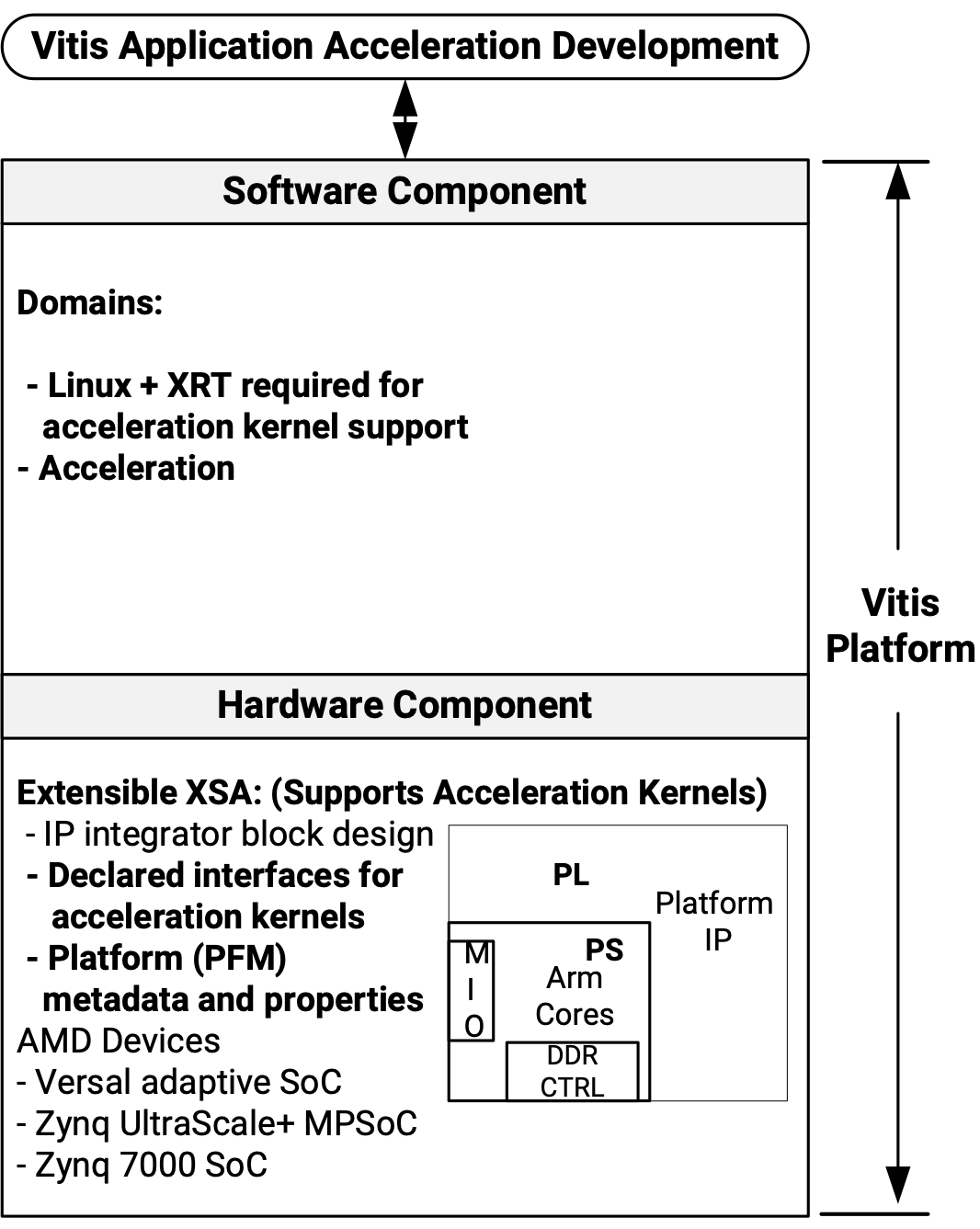

a Vitis extensible platform which serves as an abstraction of the PL hardware to the host application development process, and the platform is composed of

a domain with the necessary software to run Linux on the PS host

a base PL hardware block with a predefined configuration of AXI4 interfaces for PL kernel control by the PS host and for data transfer between the PS host and the PL kernels via global memory, clocks, and interrupt signals

Fig. 1.4 Components of a Vitis extensible platform (image taken from [AMD-Xilinx23a])#

PL kernels that implement DSP objects and algorithms

a predefined configuration of AXI4 interfaces for kernel control and data transfer, clock input, and interrupt signals to which each PL kernel must conform,

a host application program that controls the PL kernels, and passes input to and retrieves output from the PL kernels, and

the Xilinx Runtime (XRT) library which contains Linux drivers and APIs to support PL kernel control and data transfer in host application programming.

In addition, Vitis HLS can be employed to automatically synthesize interfaces that conform to the predefined configuration required by VAAD for a PL kernel.

The tradeoffs for adopting VAAD are potential losses in flexibility of the implementation architecture, low-level control of the PL resources, and PL utilization efficiency. Nonetheless, these potential losses are rather acceptable for us since we will not be interested in developing interfaces to other peripherals, and the adoption of VAAD allows us to focus only on the “DSP stuff” in our development.

1.3.2. VAAD Procedures in Vitis#

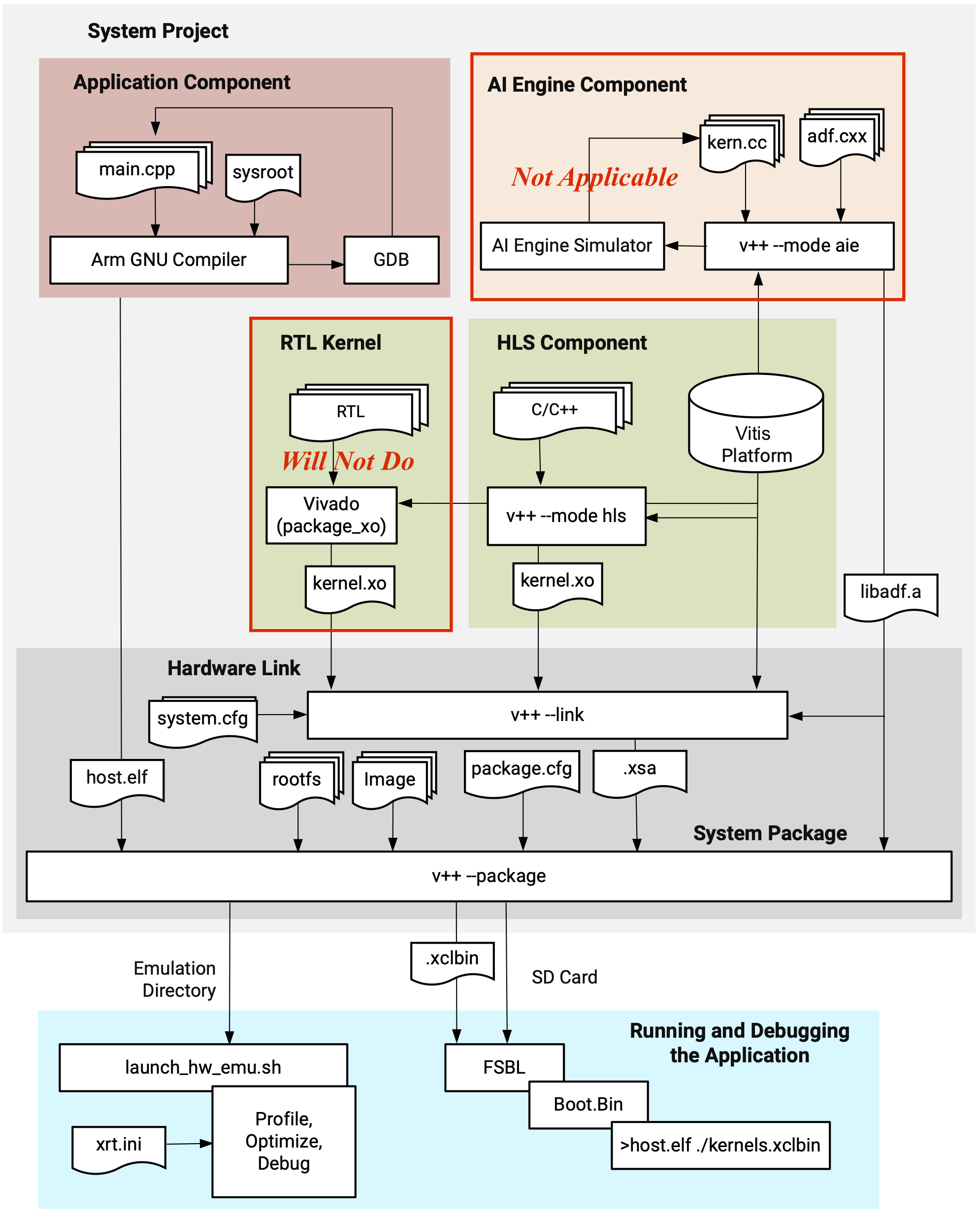

The followings are the steps of performing our DSP development under VAAD:

Build a Vitis extensible platform for the RFSoC 4x2 board:

Use Vivado to build a hardware platform component

Use PetaLinux to build an image, rootfs, and the corresponding SDK for the Linux domain with the required boot files, device tree, and XRT library

Create a Platform Component in Vitis to build the Vitis extensible platform

Create a System Project in Vitis by selecting to use the Vitis platform, the Linux kernel image, rootfs, and sysroot generated in step 1. The system project will serve as a system container for developing our embedded application.

Create a HLS Component (multiple HLS components) in Vitis to use Vitis HLS to develop DSP kernel(s).

Create an Application Component in Vitis to develop PS host application.

Add the HLS and application components to the system project.

Build the system project for software emulation, hardware emulation, and/or hardware in Vitis.

Deploy the host executable and FPGA bit-stream, if applicable, for testing, debugging, and verification. The usual sequence of testing build is to start from software emulation, then to hardware emulation, and finally to hardware.

Note that steps 2-5 can be replaced, and often simplified, by generating all the components from an Acceleration Example in Vitis and modifying the corresponding components in the example.

Fig. 1.5 VAAD Procedures in Vitis (image modified from [AMD-Xilinx23a])#

1.3.3. Class Vitis Extensible Platform#

To ease the development process, I have built a simple Vitis extensible platform described in step 1 of Section 1.3.2 for use in class. The platform is called

eee4511c_vitis_platformand will be provided. Those interested may follow the steps similar to those in this tutorial to generate the Vitis platform (for Vivado and Vitis v2023.2).The

eee4511c_vitis_platformhas ADC-D (ADC0 on tile 224) on the RFSoC4x2 board enabled at sampling rate \(307.2\) Msps. It also provides two clocks at \(200\) MHz and \(400\) MHz to drive the PL kernels. For all examples discussed in the later sections, we use the \(200\) MHz clock as the main clock to drive every PL kernel. The block diagram of the hardware platform component generated by Vivado is given below:

Fig. 1.6 Hardware platform component of eee4511c_vitis_platform#